# HCDデータの審査について

全脳アーキテクチャ・イニシアティブ 山川 宏

## なぜBRAデータを審査する必要があるのか?

脳型ソフトウェアの仕様情報であるHCDを、次のような応用領域に用いるには、高い生物学的妥当性が望まれる。

- Dysfunction再現による医療応用

- 対人インタラクションの設計

- ▼ マインド・アップロードの器

- ML技術の統合による脳型AGI開発

審査により一定程度以上の妥当性をもつHCDデータを 登録/公開する仕組みを構築中

# 審査対象となるHCD資料一覧(三点セット)

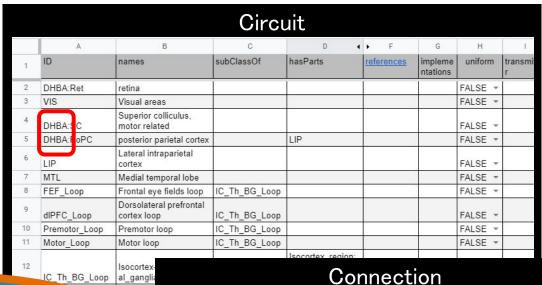

| ファイル                       | 概要                                                                                                                                                             |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HCD<br>descriptive<br>text | TLFを解剖学的構造に対して矛盾なく、どのように分解したのか」をトップダウンに説明する。<br>※フォーマットは、HCD Descriptive Text: Project ID (Template)                                                           |

| HCD image                  | ROIに含まれるCircuit/Uniform Circuitの解剖学的構造、およびROIに対する入力および出力をノードとリンクで表現した図。 ※ Draw.ioなどの作図ツール作成した画像ファイル                                                            |

| HCD data                   | ROIに含まれるCircuit/Uniform Circuit、Uniform Circuit間の<br>Connection、Uniform Circuitに割り当てられた計算上の意味や計算<br>プロセスを記したファイル。<br>※作成方法はHCD data preparation manual-jp に基づく |

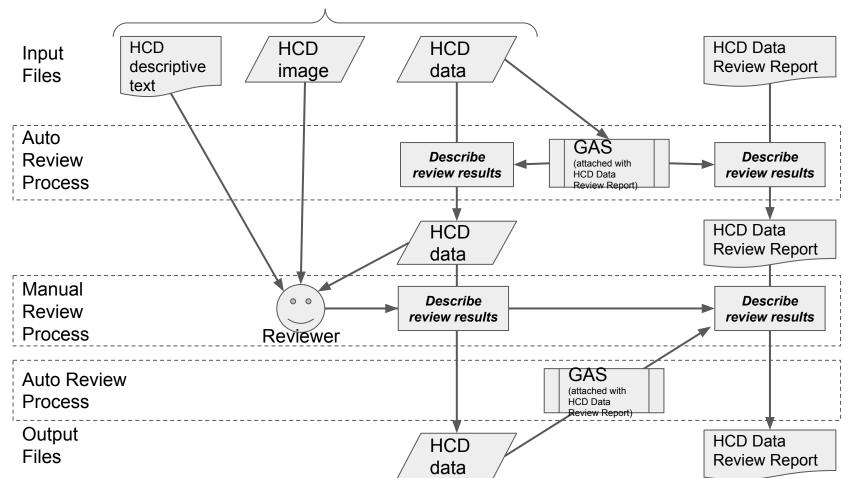

#### 審査フロ一図

#### HCD作成者が準備する3点セット

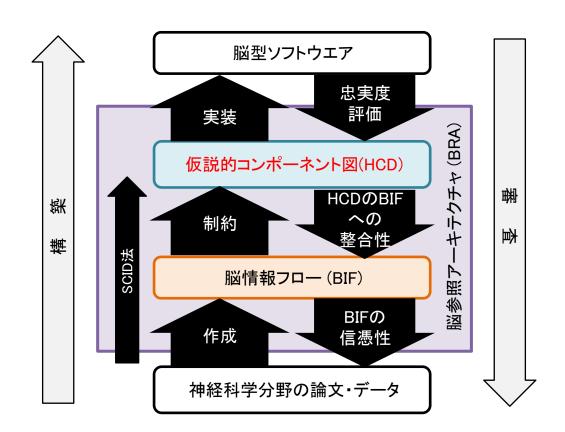

# BRA駆動開発

# BRAの審査

#### 審査観点:BRAが満たすべき3つの性質

#### HCDの機能性

コンポーネントのプロセスの連鎖により 機能を発揮できる

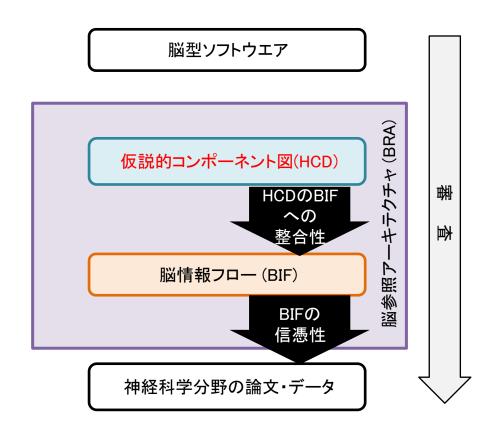

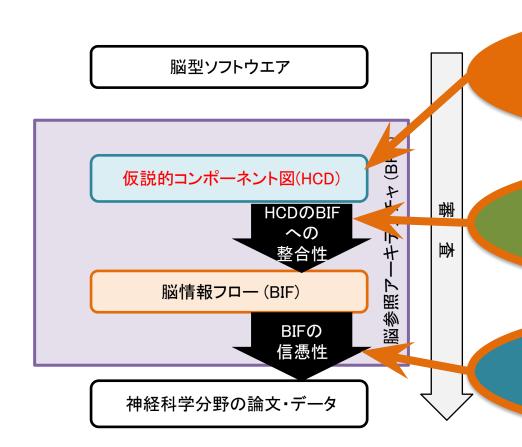

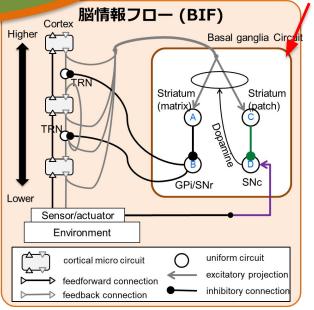

### HCDのBIFへの整合性

HDC内の全ての構造要素が、BIFの構造 に対応づいている

#### BIFの信憑性

記述された解剖学的構造等が文献や データで支持されている

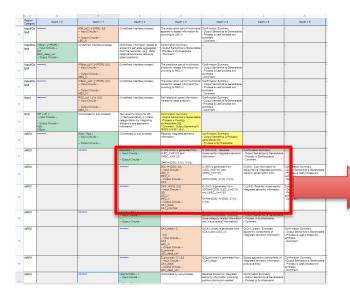

### 適切度評価: BIFの信憑性(形式審査)

### BIFの信憑性

記述された解剖学的構造等が文献や データで支持されている

|   | Isocortex       |    |                |                 |               |                |                 |              |

|---|-----------------|----|----------------|-----------------|---------------|----------------|-----------------|--------------|

|   | Thalamus        |    | А              | В               | C 4           | ▶ E            | F               | G            |

|   | gar             | 1  | inputCircuit = | outputCircuit = | transmitter = | reference =    | implementations | modType      |

|   | i i             | 2  | DHBA:Ret       | VIS             |               | Hikosaka,2000  |                 | Excitatory * |

|   |                 | 3  | VIS            | MTL             |               | O'Reilly,2020  |                 | Excitatory * |

|   | nuc<br>(anglia) | 4  | VIS            | LIP             | 1             | Hikosaka,2000  |                 | Excitatory * |

|   | thalamus        | 5  | VIS            | DHBA:PoPC       |               | Hikosaka,2000  |                 | Excitatory * |

| 9 |                 | 6  | DHBA:PoPC      | MTL             | 1 1           | O'Reilly,2020; | avitz,2011      | Excitatory * |

|   |                 | 7  | LIP            | FEF_Loop        |               | Hikosaka,2000  |                 | Excitatory * |

|   |                 | 8  | FEF_Loop       | LIP             |               | Hikosaka,2000  |                 | Excitatory * |

|   |                 | 9  | FEF_Loop       | dIPFC_Loop      | , a           | Hikosaka,2000  |                 | Excitatory * |

|   |                 | 10 | FEF_Loop       | DHBA:SC         | 1             | Hikosaka,2000  |                 | Excitatory * |

|   |                 | 11 | MTL            | dIPFC_Loop      |               | Passingham,2   | 12              | Excitatory * |

|   |                 | 12 | dIPEC Loop     | MTI             |               | Passingham 2   | 12              | Excitatory * |

### 適切度評価: HCDのBIFへの整合性

#### HCDの構造要素がROI内の構造に対応づく

⊆ircuit: A,B,C,Dが夫々に対応

ction: 上記Circuit間の接続と向きが対応

ROI

HDC内の全ての構造要素が、BIFの構造 に対応づいている

HCDのBIFへの整合性

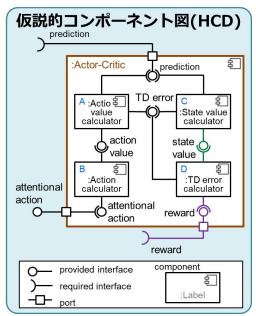

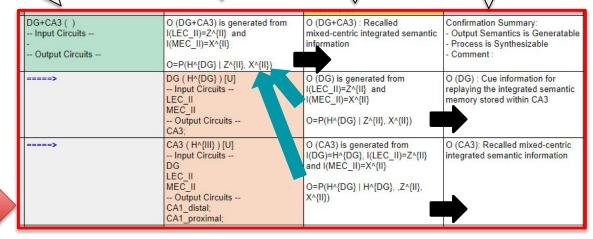

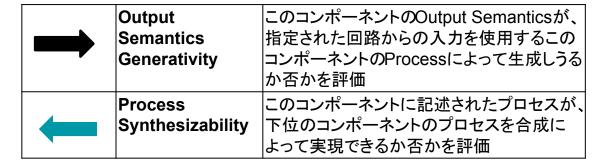

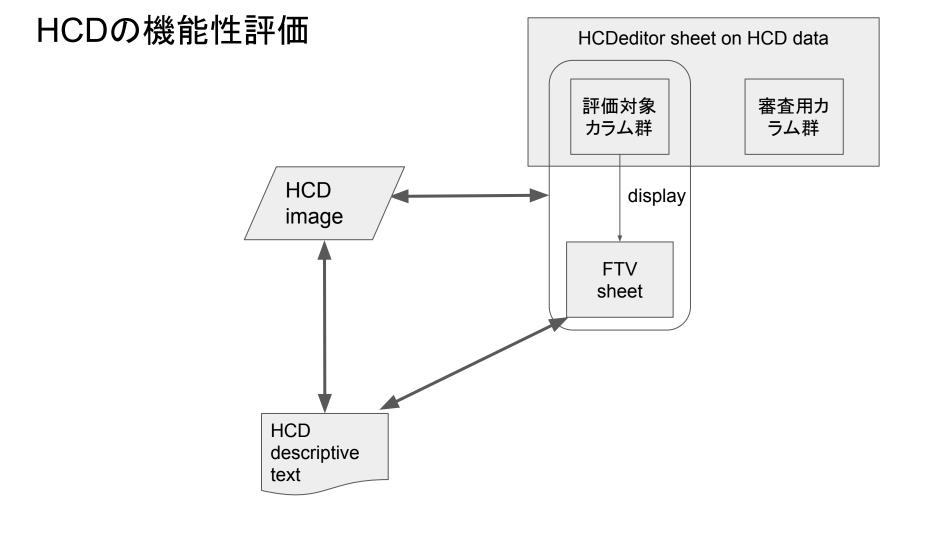

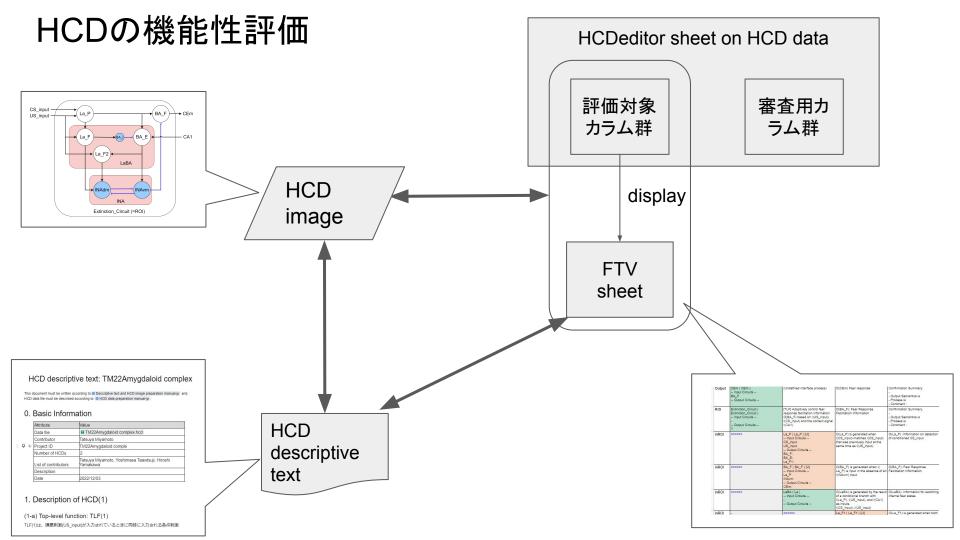

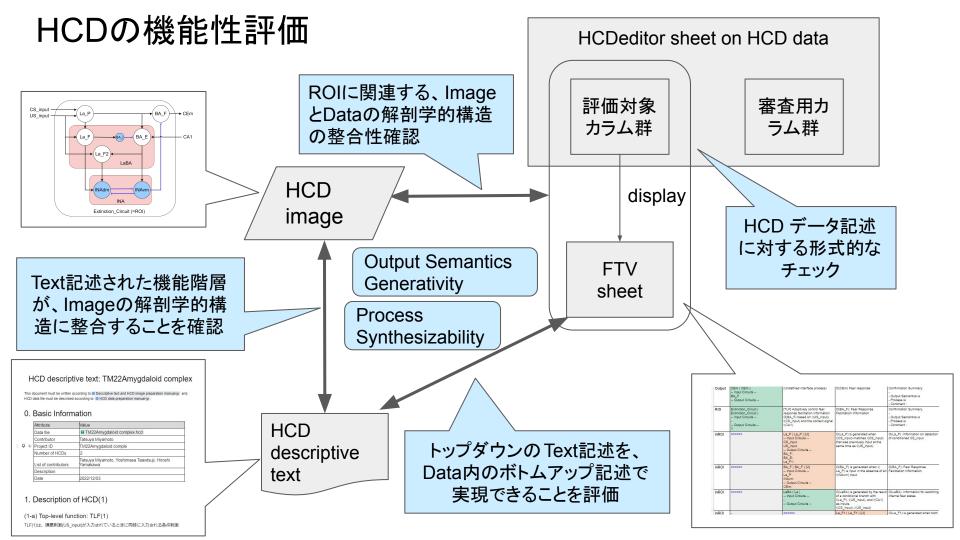

# HCDの機能性評価

# HCDの機能性

コンポーネントのプロセスの連鎖 により機能を発揮できる

HCDを構成する、コンポーネントが担うプロセスの連鎖によってROIが担う目的(TLF)を達成できることを、情報分野の専門家は判断する。

|    | D                  | E                                                                          | F                                                                                                                                       | G                                                                                                                                                | Н                                                                                                                                   | T.                                                                                             | J                                                                    |

|----|--------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 1  | Region<br>Category | Depth = 0                                                                  | Depth = 1                                                                                                                               | Depth = 2                                                                                                                                        | Depth = 3                                                                                                                           | Depth = 4                                                                                      | Depth = 5                                                            |

| 2  | Input              | US_input ( ) [U] Input Circuits Output Circuits La_P; La_F1; La_F2;        | (Undefined interface process)                                                                                                           | Unconditioned stimulus                                                                                                                           | Confirmation Summary:  - Output Semantics is - Process is - Comment :                                                               | -                                                                                              | -                                                                    |

| а  | Input              | CS_input ( ) [U] Input Circuits Output Circuits La_P:                      | (Undefined interface process)                                                                                                           | Conditioned stimulus                                                                                                                             | Confirmation Summary: - Output Semantics is - Process is - Comment :                                                                | -                                                                                              | -                                                                    |

| 4  | Input              | CA1 ( ) Input Circuits Output Circuits BA_E:                               | (Undefined interface process)                                                                                                           | Context                                                                                                                                          | Confirmation Summary: - Output Semantics is - Process is - Comment :                                                                | -                                                                                              | -                                                                    |

| 5  | Output             | CEm ( CEm ) Input Circuits BA_F Output Circuits                            | (Undefined interface process)                                                                                                           | O(CEm) Fear response                                                                                                                             | Confirmation Summary: - Output Semantics is - Process is - Comment :                                                                | -                                                                                              | -                                                                    |

| 6  | ROI                | Extinction_Circuit ( Extinction_Circuit ) Input Circuits Output Circuits ? | [TLF] Adaptively control fear response facilitation information O(BA_F) based on I(US_Input), I(CS_input) and the context signal I(CA1) | O(BA_F): Fear Response<br>Facilitation Information                                                                                               | Confirmation Summary: - Output Semantics is - Process is - Comment :                                                                | - 0                                                                                            | •                                                                    |

| 7  | inROI              | ====>                                                                      | La_F' ( La_F' ) [U] Input Circuits CS_input US_input Output Circuits BA_F; BA_E: La_F1;                                                 | O(La_P) is generated when I(CS_input) matches I(CS_input) that was previously input at the same time as I(US_input).                             | O(La_P) :Information on detection of conditioned CS_input                                                                           | Confirmation Summary: - Output Semantics is - Process is - Comment :                           |                                                                      |

| 卞  | ンて                 | ·ト                                                                         | BA_F (BA_F ) [U] Input Circuits La_P INĀvm Output Circuits CEm;                                                                         | O(BA_F) is generated when I(<br>La_P) is input in the absence of an<br>I(INAvm) input                                                            | O(BA_F): Fear Response<br>Facilitation Information                                                                                  | Confirmation Summary: - Output Semantics is - Process is - Comment :                           |                                                                      |

|    | て                  | -                                                                          | LaBA ( La ) Input Circuits Output Circuits                                                                                              | O(LaBA) is generated by the result<br>of a conditional branch with<br>I(La_P), I(US_input), and I(CA1)<br>as inputs.<br>I(CS_input), I(US_input) | O(LaBA): Information for switching internal fear states                                                                             | Confirmation Summary: - Output Semantics is - Process is - Comment :                           |                                                                      |

| -  | で                  | き                                                                          | ====>                                                                                                                                   | La_F1 (La_F1) [U] Input Circuits US_input La_P Output Circuits BA_L; INAdm;                                                                      | O(La_F1) is generated when both I(La_F) and I(US) were input.                                                                       | O(La_F1): Information on<br>simultaneous detection of<br>conditioned CS_inptut and<br>US_input | Confirmation Summary:                                                |

| 多  | :15                | I                                                                          | >                                                                                                                                       | La_F2 ( La_F2 ) [U] Input Circuits US_input BA_E Output Circuits INAdm;                                                                          | O(La_F2) is generated when both I(BA_E) and I(US) inputs are provided.                                                              | O(La_F2): Reinstatement<br>Facilitation Information                                            | Confirmation Summary: - Output Semantics is - Process is - Comment:  |

|    |                    |                                                                            | 22222>                                                                                                                                  | BA_E ( BA_E ) [U] Input Circuits CA1 La_P BA_I Output Circuits INAvm, La_F2;                                                                     | O(BA_E) is generated when context I(CA1) matches a previously received I(CA1) with I(I(La_P) in the absence of an input of I(BA_I). | O(BA_E): Low fear facilitation<br>Information                                                  | Confirmation Summary: - Output Semantics is - Process is - Comment : |

| 13 | inROI              | •                                                                          | ====>                                                                                                                                   | BA_i (BA_i) [U] - Input Circuits La_F1 - Output Circuits BA_E:                                                                                   | O(BA_i) is generated when I(La_F2) is input                                                                                         | O(BA_i): Information on<br>simultaneous detection of<br>conditioned CS_inptut and<br>US_input  | Confirmation Summary: Output Semantics is - Process is - Comment :   |

### HCDの機能性評価

#### HCDデータ

Circuit ID、ラベル 入力、出力 プロセス (実装の対象) 出力の意 味

審査結果

#### 主な審査観点

機能のツリー表示

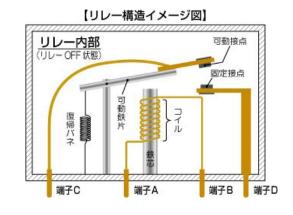

# 参考: Process Synthesizability で審査する観点

#### 目的を達成する実行可能な仕組みがが構築できているか

#### <u>リレーON動作</u>

動作機序 実行可能 な方法の 論理

- <sup>--</sup>1.『電装品スイッチ』を入れます(=ONする)

- 2. 『端子A』~『端子B』間に電気(小電流)が流れます

- 3.『コイル』へ電気が流れます

- 4.『コイル』に磁場が発生します

- 5. 『鉄芯』に磁力が生じて磁石となります

- 6. 『鉄芯』が『可動鉄片』を引き寄せます

- 7.『可動接点』が『固定接点』と接触します

- 8.『端子C』~『端子D』間がつながります

- └9.『バッテリー(+)』から『電装品』へ電気が供給されます

<u>且的</u>

─ 10. 『電装品』が動作を開始します

参考: MITSUBASANKOWA, リレーの構造と動作原理, https://www.mskw.co.jp/support/car/relay

一般の人工物は、外界を参照した表現ではないためOutput Semanticsは議論できない。